3 Logique combinatoire (partie 2)

Table des matières

Comme le TP précédent, celui-ci est à préparer individuellement avant la séance et un compte-rendu individuel sera exigé à la fin de la séance}

3.1 Réalisation de circuits arithmétiques

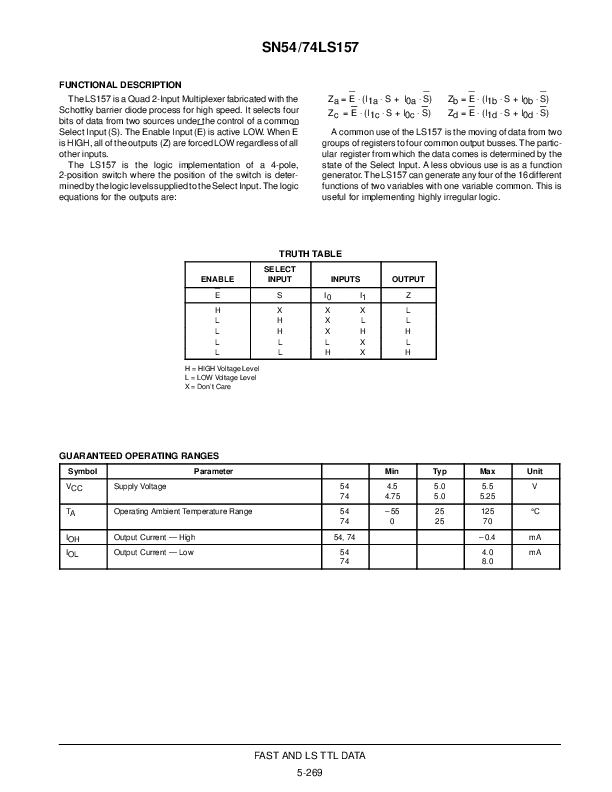

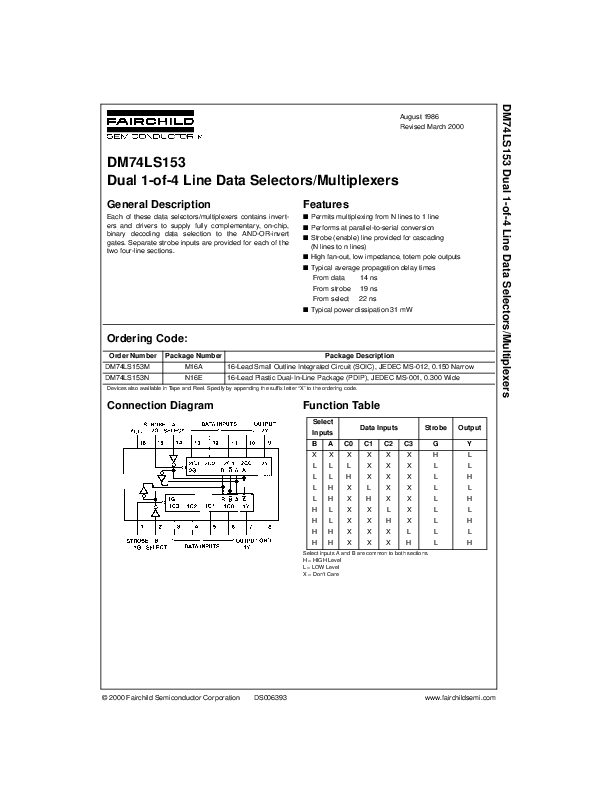

Vous pourrez utiliser les circuits du TP précédent et des circuits à plus haute densité d'intégration MSI comme les 4xMUX 2/1 74LS157 et 2xMUX 4/1 74LS153.

Pour chacune de ces questions, vous allez concevoir un système et à cette fin vous devrez suivre les étapes suivantes : établir la table de vérité, établir la table de Karnaugh pour obtenir des équations simplifiées, dessiner le schéma, dessiner de cablâge, câbler sur les platines puis tester en utilisant les LEDs.

- Réalisez un additionneur de mots A et B de 2 bits qui prenne en compte la retenue amont \(C_{-1}\) et fournit la retenue aval \(C\). Validez et testez votre montage sur la platine.

- En conservant le montage de la question précédente, réalisez un additionneur 2 bits commandé avec deux modes :

- mode passeur : si le bit de commande vaut 0, la sortie du système vaut l'entrée A et la retenue amont est propagée ;

- mode additionneur : si le bit de commande vaut 1, la sortie du système vaut \(A+B\).

- En utilisant que des multiplexeurs et des inverseurs, réalisez la fonction « majorité » entre les valeurs de 3 entrées (par exemple, la sortie vaut 0 si une majorité d'entrées est à 0).

3.2 Circuits à disposition

Pour ce TP vous pouvez utiliser les circuits intégrés du TP précédent mais aussi ces deux nouveaux circuits MSI dont le brochage et fonctionnement sont détaillés dans le feuille ci-dessous.