3 Logique combinatoire

Table des matières

3.1 Objectif

L'objectif de ces séances de travaux pratiques est de vous familiariser avec des circuits intégrés élémentaires (portes logiques) de faible densité (dizaine de transistors) dit SSI (Small Scale Integration) afin de réaliser des fonctions numériques simples. Ces TPs sont à préparer individuellement avant la séance et un compte-rendu individuel sera exigé à la fin de la séance.

3.2 Travail préliminaire, compte-rendu

Le compte-rendu qu'il vous est demandé de rendre en fin de séance consiste en la rédaction sur feuilles de la préparation du TP à laquelle s'adjoint les corrections et compléments éventuels issus de la manipulation pratique.

La préparation elle-même consiste à répondre aux questions du TP avec, quand cela a un sens, le suivi des étapes suivantes : établir la table de vérité, établir la table de Karnaugh pour obtenir des équations simplifiées, dessiner le schéma avec les portes logiques, dessiner le câblage avec les circuits intégrés en indiquant et respectant leur brochage.

La phase de manipulation en TP ne servira en principe qu'à valider par la réalisation du câblage réel le travail théorique issu de la préparation.

3.3 Présentation du matériel

Pour réaliser les manipulations de ce TP, vous avez à votre disposition une platine contenant des supports pour circuits intégrés, des LEDs, des afficheurs, des boutons poussoirs avec et sans maintien ainsi que divers points de connexion.

Les platine de manipulation doivent être alimentées par une tension continue de +5V. À cette fin, des alimentations de +5V sont mises à votre disposition. Un premier travail à faire avant de débuter la séance est de tout d'abord vérifier avant branchement que la tension délivrée par l'alimentation est bien de +5V continue. En effet, les composants ne supporteraient pas une tension inadaptée. Par la suite, vous n'alimenterez la platine qu'au moment de tester, aucunement pendant le câblage pour éviter tout court-circuit.

La platine comporte 7 supports pour circuits intégrés. Afin de câbler plus facilement, des prises pour fils électriques fins sont disposées autour du support, leur position respectant la disposition des broches du support. Il y a 2 prises par broche. de chaque côté du support se trouve un arrivée d'alimentation. Le support peut être plus large que le circuit intégré qui y sera placé. Par convention, on placera le circuit en buté à droite sur le support avec le détrompeur du circuit sur la gauche.

3.4 Échauffement

- Prenez une alimentation et vérifier que sa tension de sortie est bien de +5V continue.

- Pour se familiariser avec le matériel à votre disposition, vous allez tout d'abord dans cette question réaliser un montage simple impliquant quelques circuits intégrés. Vous allez vérifier une des lois de De Morgan : \(\overline{a+b} = \bar{a}.\bar{b}\). Pour cela vous allez comparer simultanément la sortie des deux fonctions logique \(f_1 = \overline{a+b}\) et \(f_2=\bar{a}.\bar{b}\). Les entrées de chaque fonction seront reliées à des boutons poussoirs avec maintien, et l'état logique des sortie sera visualisé à l'aide de LEDs.

3.5 Réalisation de circuits combinatoires simples

Pour chacune de ces questions, vous allez concevoir un système et à cette fin n'oubliez pas que vous devrez suivre les étapes suivantes : établir la table de vérité, établir la table de Karnaugh pour obtenir des équations simplifiées, dessiner le schéma, dessiner le câblage, câbler sur les platines puis tester en utilisant les LEDs et boutons poussoirs.

- Réalisez un inverseur commandé (pour une entrée E, si la commande C=1 alors la sortie \(S=\overline{E}\), sinon \(S=E\)).

- Réalisez un multiplexeur 2 vers 1.

- Réalisez un encodeur prioritaire (poids le plus fort) 4 vers 2 (si deux entrées sont actives, on n'encode que celle de poids le plus fort). Conservez le montage pour les deux questions suivantes. Comment gérer l'ambiguïté dans l'encodage entre la présence d'une valeur sur l'entrée 0 et l'absence de valeur toutes les entrées ?

- Réalisez un décodeur binaire sur 2 bits 2 vers 4 (fonction inverse de l'encodeur précédent).

- Validez le fonctionnement du système combiné encodeur-décodeur des deux questions précédentes afin d'obtenir la fonction identité (modulo le poids prioritaire).

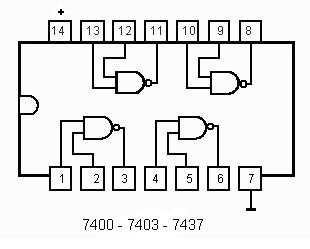

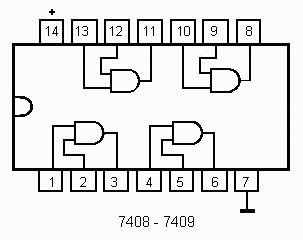

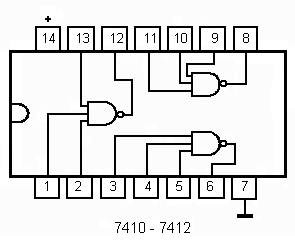

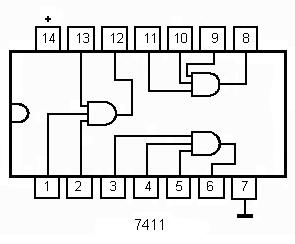

3.6 Circuits à disposition

Un ensemble de circuits intégrés sont mis à votre disposition dans salle pour réaliser ce TP. Le tableau suivant les regroupe avec le détail de leur brochage.