1 Logique combinatoire et séquentielle

Table des matières

1.1 Introduction

Dans ce TP nous allons reprendre le même principe que pour le TP de logique combinatoire du premier semestre, mais en utilisant cette fois un logiciel de simulation et non des circuits réels.

1.2 Réalisation de circuits arithmétiques

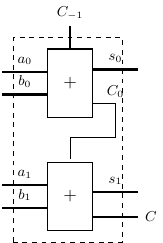

Nous voulons réaliser un additionneur de deux mots A et B de 2 bits chacun qui prenne en compte un retenue amont \(C_{-1}\) et fournit le résultat S sur 2 bits et la retenue aval \(C_1\).

Pour le réaliser, vous allez décomposer le problème en deux sous-additionneurs 1 bit identiques afin d'appliquer l'algorithme d'addition usuel :

- on ajoute d'abord les unités,

- puis on passe aux dizaines avec retenue éventuelle.

On sera ainsi facilement capable d'augmenter le nombre de bits de notre additionneur sans devoir reconcevoir tout un nouveau système complexe.

Établissez la table de vérité d'un additionneur 1 bit à 3 entrées (A, B, C_in) et deux sorties (S et C_out),

Déterminer les équations de S et de C_out par la méthode de Karnaugh

À l'aide du logiciel LogiSim, voir Description du logiciel, réalisez le montage en utilisant uniquement les circuits TTL des portes logiques de base du TP de logique combinatoire.

Ajoutez un nouveau circuit («Projet->Ajouter un circuit ...») que vous nommerez Add1B,

Sélectionnez ce nouveau circuit pour y réaliser l'additionneur 1 bit demandé,

Utilisez les broches d'entrée pour les entrées et les broches de sortie pour les sorties. Pour pouvez ajouter en plus des LEDs pour visualiser plus facilement le résultat,

Astuce : activez « afficher la structure interne » des circuits TTL pour connaître le sens des broches du circuit TTL.

testez le fonctionnement correct de votre montage et faites valider par votre encadrant.

Dans le circuit principal (main), combinez deux de vos circuits Add1B afin d'avoir un additionneur 2 bits complet : 5 entrées - un mot A composé des bits A1 (poids fort) et A0 (poids faible), - un mot B composé des bits B1 et B0, - un retenue amont C_in.

3 sorties - un mot S composé des bits S1 et S0, résultats de l'addition, - une retenue aval C_out

Testez votre montage et faites valider.

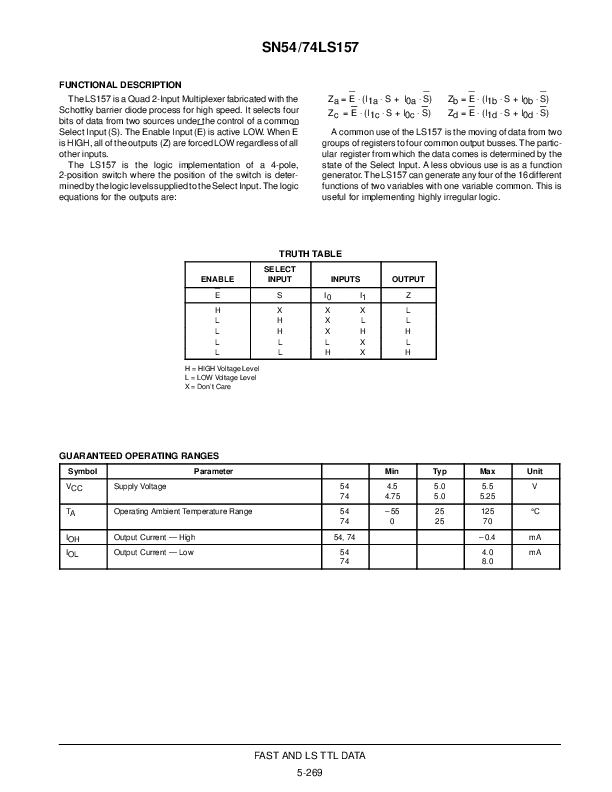

En complétant le montage principal de la question précédente et en utilisant le ou les 4xMUX 2/1 74LS157 (description dans la section Circuits TTL à disposition), réalisez un additionneur 2 bits commandé avec deux modes :

- mode passeur : si le bit de commande K vaut 0, la sortie R du système (sur 3 bits) vaut l'entrée A et la retenue amont C_in est propagée ;

- mode additionneur : si le bit de commande K vaut 1, la sortie R du système vaut \(A+B+C_in\).

Testez votre montage et faites le valider.

Pour rappel, un multiplexeur 1 bit \(2^n\) vers 1 est un circuit avec une entrée de sélection K sur n bits, \(2^n\) entrées \(I_0 , . . . , I_{2^n-1}\) sur 1 bit, et une sortie R sur 1 bit ; le signal R est égal à l'entrée \(I_m\) lorsque K vaut \(m\) (en binaire sur n bits). Ci-dessous un exemple de multiplexeur 4 vers 1, 1 bit.

1.3 Logique séquentielle

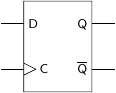

vous devez cette fois réalisez une bascule D 1 bit avec mémorisation sur front montant.

Faites un diagramme d'états (8 états ?) de la bascule D,

Pour rappel, une bascule D possède 2 entrées (D et C) et deux sorties (Q et son inverse) :

l'entrée D où se trouve la donnée à mémoriser,

l'entrée C qui mémorise la valeur de D au moment du front montant,

la sortie Q qui délivre la valeur mémorisée.

Faites la table de transition associée,

Réduisez si possible cette table,

Établissez les équations des bits de la fonction de transition d'état (par Karnaugh),

Établissez l'équation de la fonction de sortie,

Réalisez dans le logiciel le montage toujours en utilisant uniquement les circuits TTL des portes logiques de base du TP de logique combinatoire.

- Ajoutez un nouveau circuit («Projet->Ajouter un circuit ...») que vous nommerez Bascule_D,

- Sélectionnez ce nouveau circuit pour y réaliser le montage de la bascule demandée,

- Utilisez les broches d'entrée pour les entrées (2) et les broches de sortie pour la sortie. Pour pouvez ajouter en plus des LEDs pour visualiser plus facilement le résultat,

Testez le fonctionnement correct de votre montage et faites valider par votre encadrant.

1.4 Mini UAL

Vous allez dans cette question combiner les différents circuits réalisés pour obtenir une mini Unité Arithmétique et Logique sur 2 bits.

Dans le circuit principal (main), #. Dupliquez le circuit Bascule_D précédent pour obtenir ce qui sera un registre accumulateur sur 2 bits, #. Reliez les 2 bits de sortie de l'additionneur commandé à l'accumulateur (les entrées D des bascules), #. Reliez la sortie de l'accumulateur à l'entrée B de l'additionneur commandé (supprimez les broches d'entrée de B), #. Mettez l'entrée de retenue amont C_in à la masse, #. Testez votre montage en réalisant les étapes suivantes:

- mémoriser le mot A dans l'accumulateur, par exemple la valeur 1,

- mémoriser dans l'accumulateur le résultat de A + l'accumulateur

- Faites valider votre montage.

Note: le montage final possède 3 entrées: A (sur 2 bits), le bit de commande de l'additionneur et l'entrée d'horloge C des bascules D.

1.5 Description du logiciel

Le logiciel qui sera utilisé est LogiSim Evolution accessible par la commande /home/partage/I22/logisim.

Le menu rapide d'accès rapide aux composants est celui-ci:

Dont la description de gauche à droite est:

- l'activation/désactivation d'éléments comme les entrées,

- le placement ou la sélection de composants,

- le câblage entre composants,

- modifier l'annotation d'un circuit,

- une entrée (broche d'entrée), équivalente aux boutons de la plaque du TP de combinatoire précédent,

- une sortie (broche de sortie),

- des portes logiques de base.

Le menu de gauche permet la sélection :

- Câblage: les alimentations

- Portes logiques

- Entrée/sortie: les LEDs pour l'affichage des résultats

- TTL: les circuits intégrés comme ceux manipulés en TP.

1.6 Circuits TTL à disposition

Pour réaliser le travail demandé dans ce sujet, vous ne devrez utiliser que les broches d'entrée et de sortie (cf. menu rapide), les portes logiques de base, les LEDs, et les circuits TTL suivants :

- ceux du premier TP de logique combinatoire : 7400, 7402, 7404, 7408, 7410, 7411, 7420, 7430, 7432, 7486,

- en plus pour ce TP : 74LS157 (4xMUX 2/1).

En aucun cas vous n'utilisez des composants « tout-fait » autres que ceux précédemment cités et ceux que vous avez développés

Description détaillée du nouveau circuit intégré 74LS157.